In the context of Industry 4.0, handwritten digit recognition plays a vital role in numerous applications such as smart banking systems and postal code detection. One of the most effective approaches to tackle this problem is through the use of machine learning and neural network models, which have demonstrated impressive accuracy and adaptability in visual pattern recognition tasks.

All Projects

You can use the filters below to restrict this based on Technology or Skills.

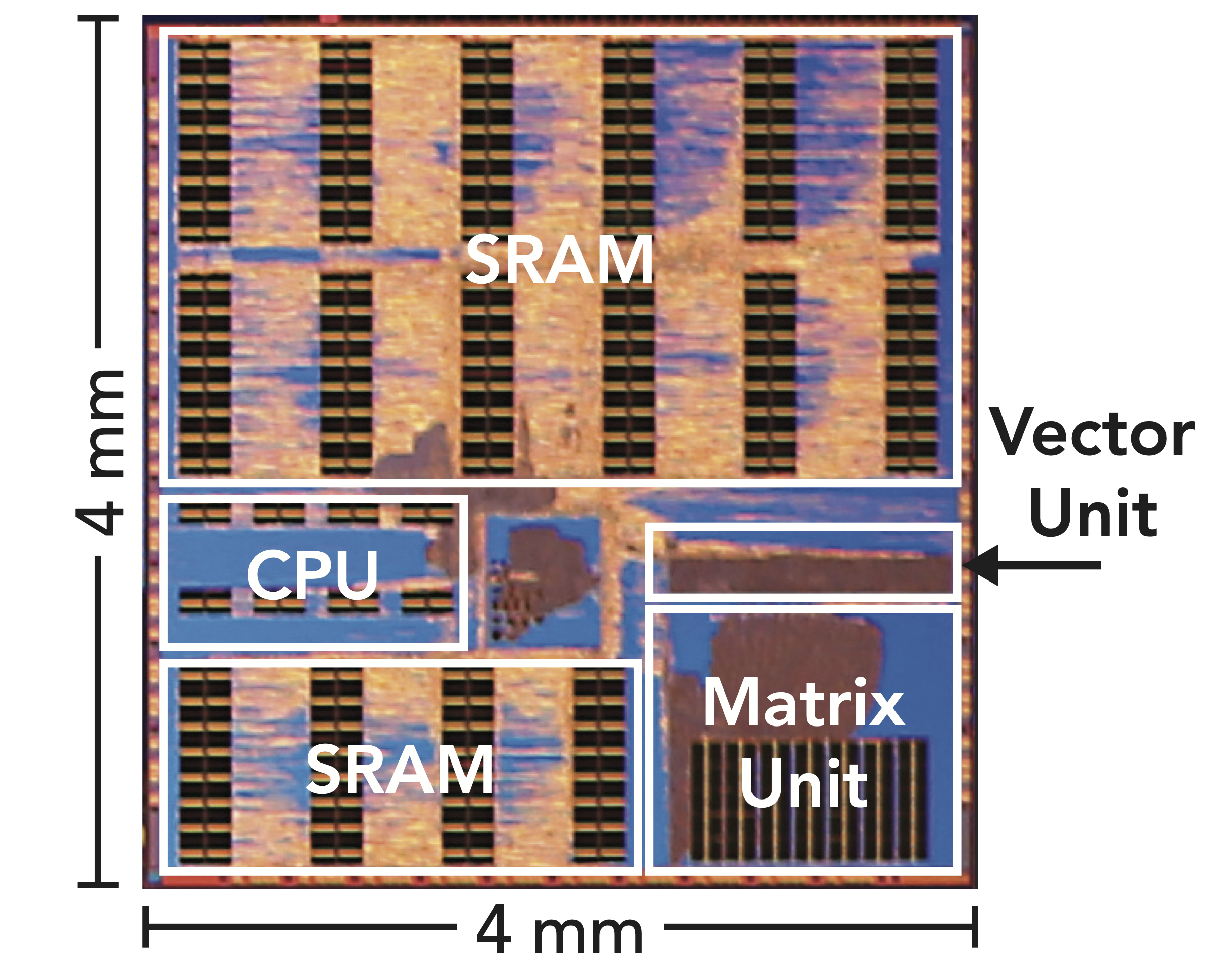

Aspen is a unified accelerator for deep neural network (DNN)-based extended reality perception workloads. Aspen proposes a mixed-precision quantization scheme using the posit datatype to reduce memory usage while maintaining accuracy, a DNN accelerator for mixed-precision posit datatypes, and efficient data prefetching and data layout to minimize data reorganization. The Aspen system-on-chip has an Arm Cortex-M3 CPU, a mixed-precision posit-based DNN accelerator, and 4 megabytes of SRAM partitioned into eight 512 KB banks, connected through a 128-bit-wide interconnect.

This program is dedicated to the development of a System on Chip (SoC) platform, specifically designed to support learning and research activities within Indonesian academic institutions. The platform serves as an educational and research tool for students, lecturers, and researchers to gain hands-on experience in digital chip design.

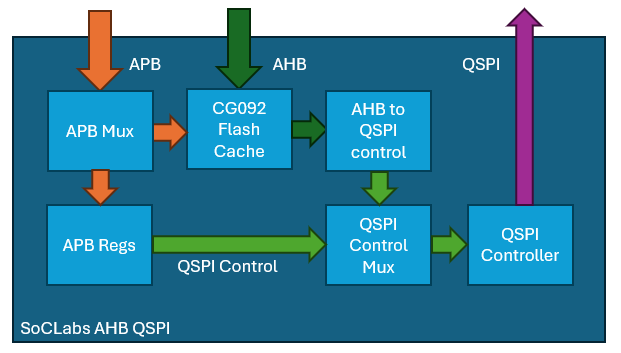

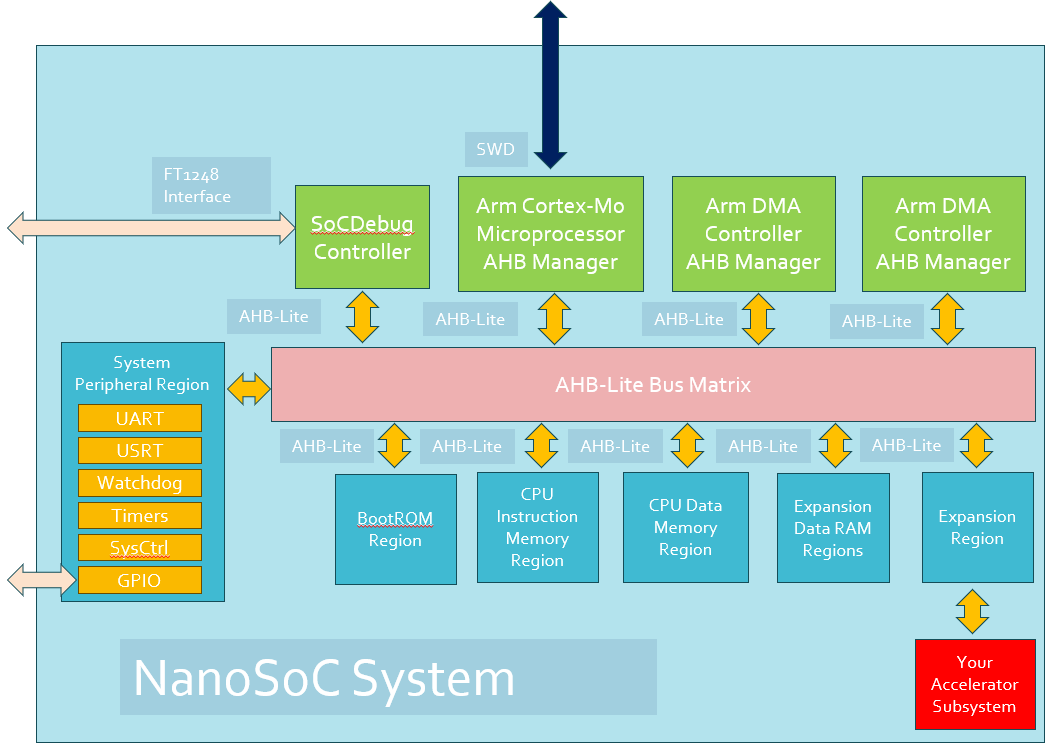

The instruction memory in the first tape out of nanosoc was implemented using SRAM. The benefit was the read bandwidth from this memory was very fast, the downside was on a power-on-reset, all the code was erased as SRAM is volatile memory. An alternative use of non-volatile memory would benefit applications where deployment of the ASIC does not allow, or simply time is not available for programming the SRAM after every power up.

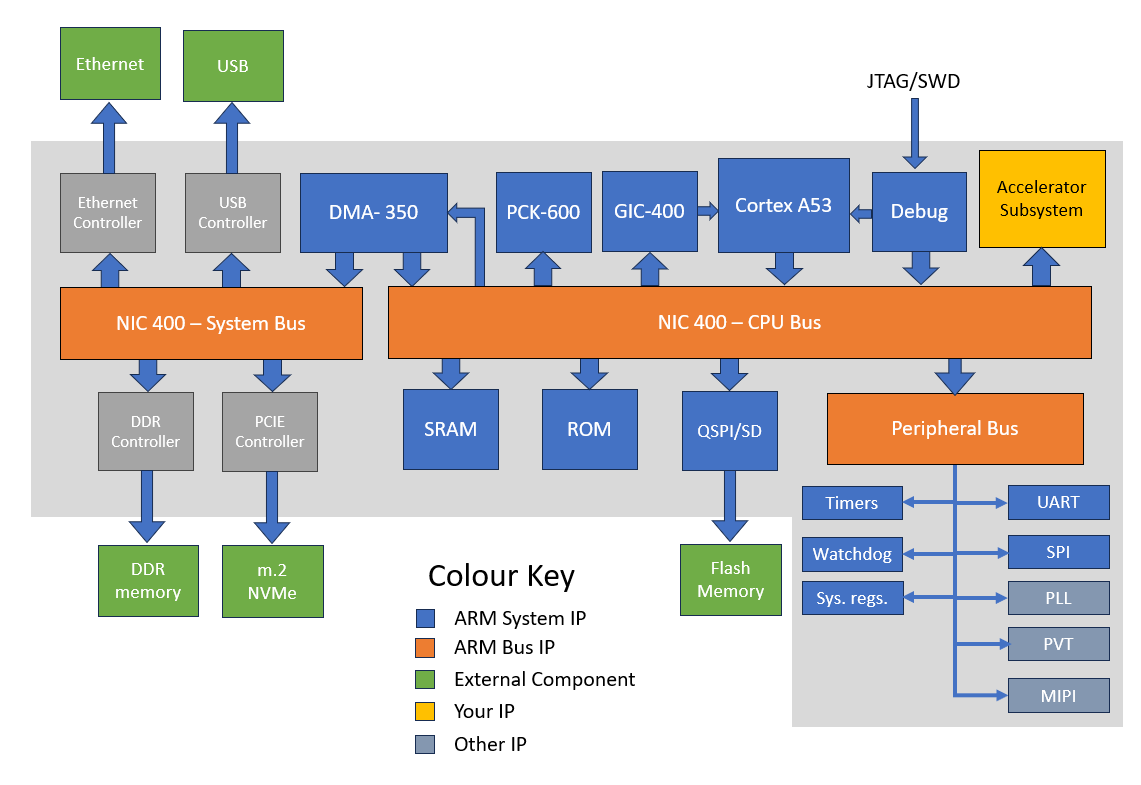

megasoc has been designed to provide a complex SoC component that can 'host' and support the development and evaluation of research components or subsystems. The design allows for seamless transition from FPGA to physical silicon implementation via a pre-verified programmable control system that allows reuse of software and diagnostic functionality to facilitate the configuration, control and diagnostic analysis of research hardware such as custom accelerators or signal processing.

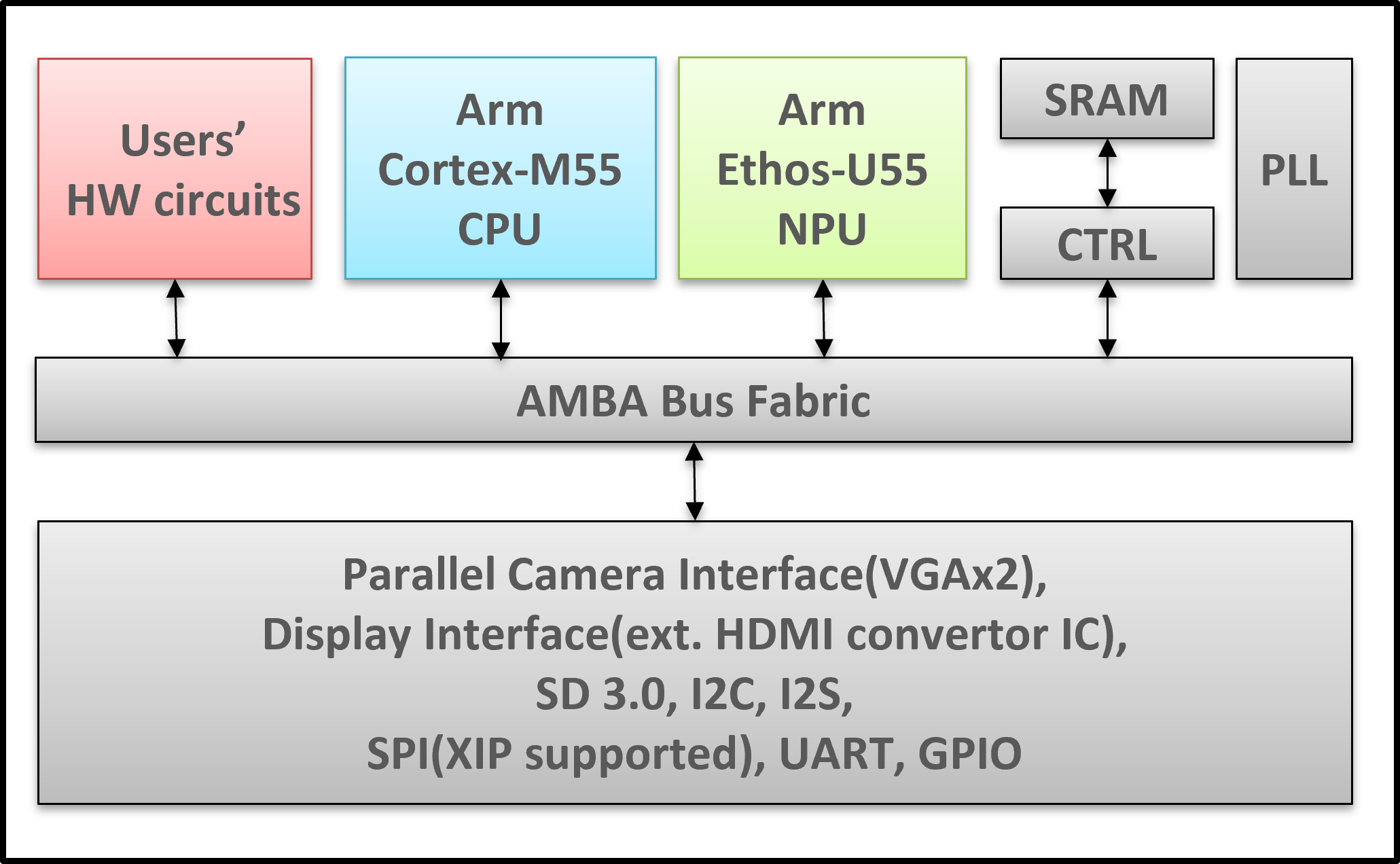

The Arm Cortex-M55 AIoT SoC design platform is an AIoT subsystem that allows custom SoC designers to integrate their hardware circuits and embedded software for differentiation. The platform is developed by TSRI (Taiwan Semiconductor Research Institute) to support academic research on SoC design. It's built on the Arm Corstone-300 reference package, featuring the Cortex-M55 CPU and Ethos-U55 NPU.

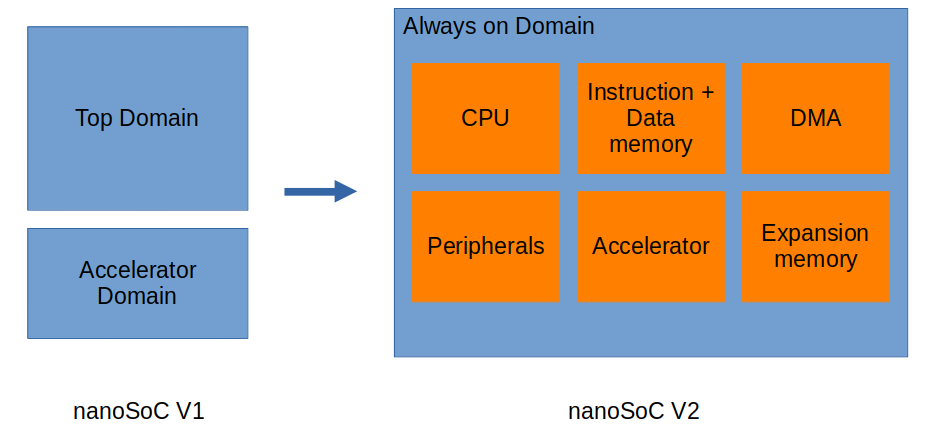

As part of plans for continued development of nanoSoC one area that requires improvement is the power structure of system. The first iteration of nanoSoC contained 2 power domains: the accelerator domain and the remainder of the SoC. Both power domains were connected to external pins to allow connection to separate external voltage regulators and power measurement ICs, as implemented in the first version of the nanoSoC testboard.

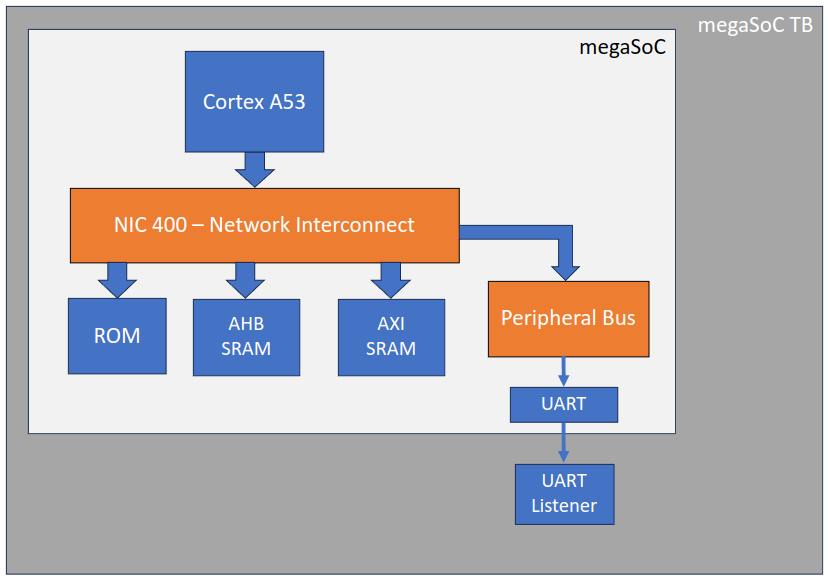

There is growing interest within the SoC Labs community for an Arm A-Class SoC that can support a full operating system, undertake more complex compute tasks and enable more complicated software directed research. The Cortex-A53 is Arm's most widely deployed 64-bit Armv8-A processor and can provide these capabilities with power efficiency.

This project aims to design and implement a high capacity memory subsystem for Arm A series processor based SoC designs. The current focus of the project is the design and implementation of a Memory Controller for DDR4 memory.

The Anh Nguyen

The Anh Nguyen

Trio Adiono

Trio Adiono

Daniel Newbrook

Daniel Newbrook

David Flynn

David Flynn

Srimanth Tenneti

Srimanth Tenneti