People

Projects

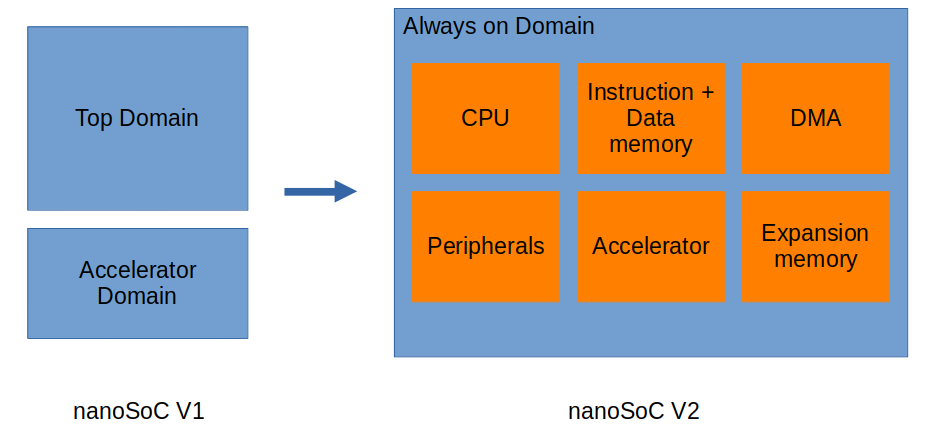

As part of plans for continued development of nanoSoC one area that requires improvement is the power structure of system. The first iteration of nanoSoC contained 2 power domains: the accelerator domain and the remainder of the SoC. Both power domains were connected to external pins to allow connection to separate external voltage regulators and power measurement ICs, as implemented in the first version of the nanoSoC testboard.

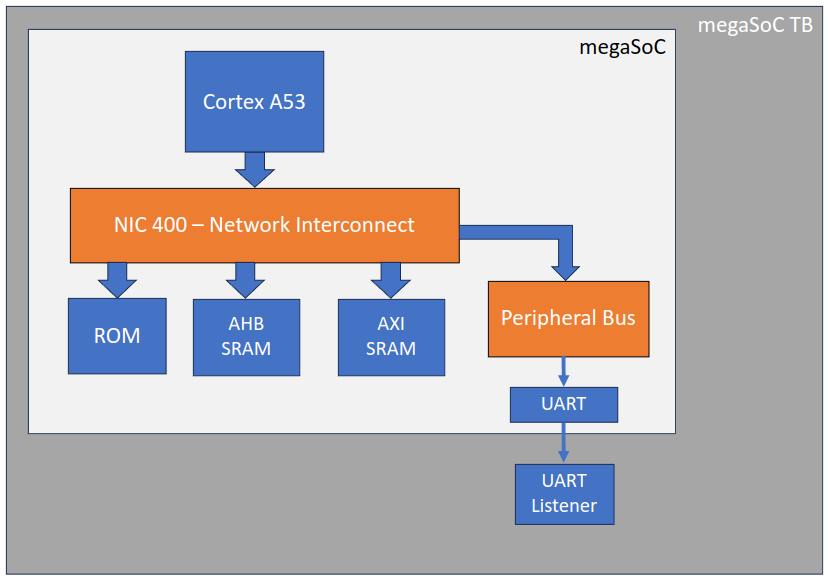

There is growing interest within the SoC Labs community for an Arm A-Class SoC that can support a full operating system, undertake more complex compute tasks and enable more complicated software directed research. The Cortex-A53 is Arm's most widely deployed 64-bit Armv8-A processor and can provide these capabilities with power efficiency.

The Synopsys HAPS® System adds additional capabilities to the FPGA-based prototyping environments SoC Labs can use to support projects. The HAPS® system provides a greater amount of logic resources supporting development of larger SoC designs. It can be used to support multiple projects simultaneously. It is used by many semiconductor companies, including arm for their CPU verification. This collaboration project will use the HAPS® system in SoC Labs projects and share with the community experience in utilising such systems.

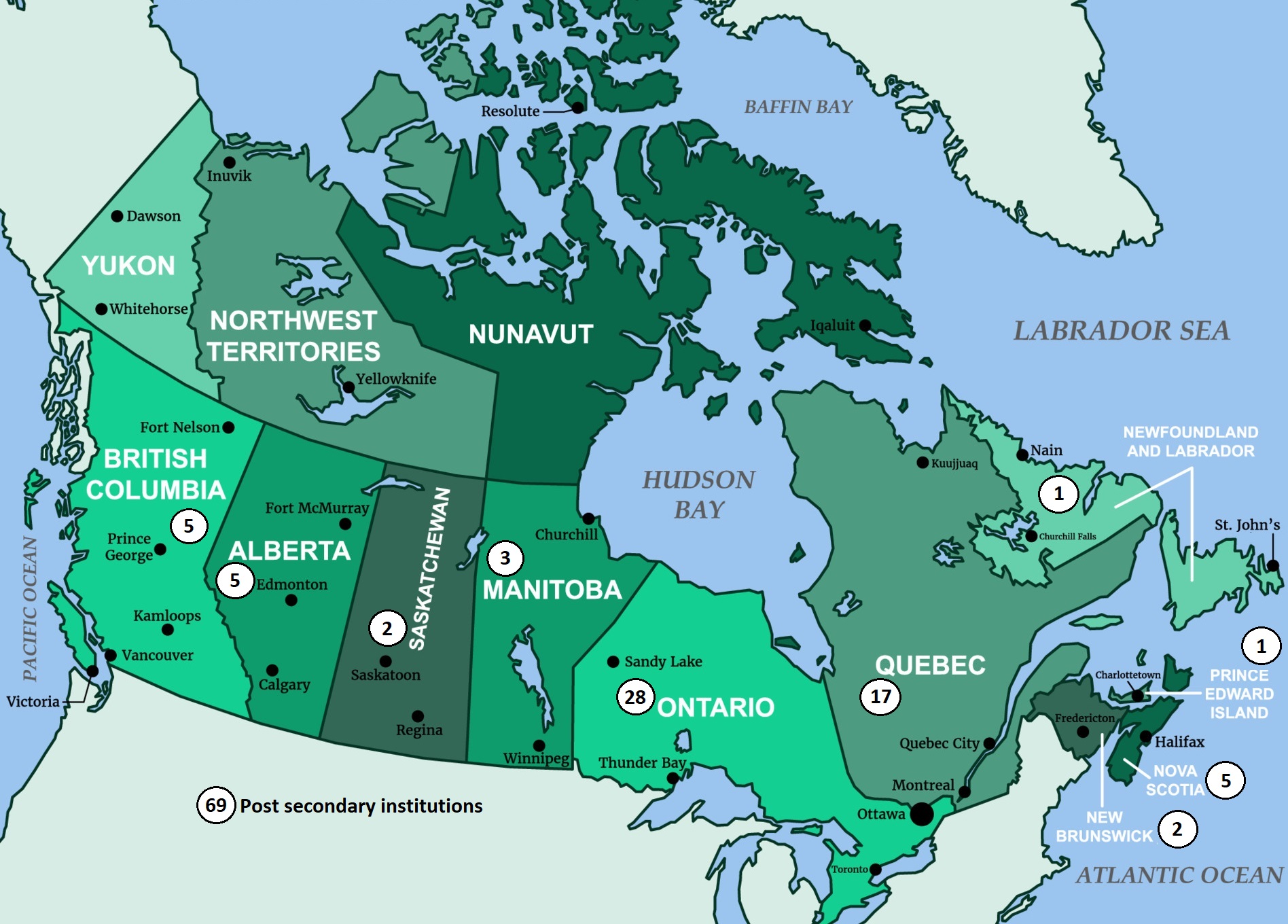

This collaboration project is aimed at providing specific tailored activities to the local geography in Canada by developing local actions that will help stimulate academics and their institutions and the broader semiconductor industry supporters to create new and exciting SoC design projects. It may include:

Daniel Newbrook

Daniel Newbrook

John Darlington

John Darlington